为下一代汽车打造ASIC的嵌入式eFPGA

对于最近研究过新车的任何人来说,很难不注意到汽车电子产品的发展是多么的迅速。仅仅将三年前的汽车安全性技术与今天的技术进行对比,您就会发现摄像头数量已显著增加,以支持诸如全景可视、驾驶员注意力分散监测器、立体视觉摄像头、前向摄像头和多个后视摄像头等应用。除了摄像头,系统功能也增强了,包括自动紧急制动、车道偏离警告、后方盲点检测和交通标志识别等。这一趋势表明,汽车电子类产品在持续快速地创新,但这也给汽车原始设备制造商(OEM)带来了全新的挑战,包括:

· 当研发一辆新车的平均时间从48个月缩短至24个月左右(请参阅缩短研发生命周期和降低设计复杂性对汽车行业的影响),同时还要支持长达10年以上的生命周期时,如何快速开发新特性和安全性功能?

· 平台架构的确定都比车辆上市提前数年,如何预测所需的硬件和软件需求?

· 当汽车用户拿消费类电子产品来做比较时,如何提高汽车电子产品的性能和质量以满足用户的期望?

专用集成电路(ASIC)解决方案

为了去解决这些问题,汽车原始设备制造商需要重新考虑他们的系统架构,并在其设计中添加灵活性,进而能够在设计过程的后期进行更改,并增加不断开发的特性和功能。这种重新设计的系统架构使原始设备制造商与其他竞争对手相比具有差异化,并为使用标准硬件器件无法解决的技术难题提供解决方案。

传统上,先进驾驶辅助系统(ADAS)架构器件的选择都依赖于现成的器件,这些器件的设计旨在支持特定的汽车安全功能和环境需求。对于诸如防抱死制动系统(ABS)等非差异化功能,这种方法是非常适合的。但是,如果您正在设计创新的安全功能,许多原始设备制造商选择构建自己的定制ASIC。与任何现成的器件相比,定制ASIC提供了最低的总体成本和最高的性能:然而,ASIC会带来风险。如果您没有确定所有必需的功能,那么您将无法进行更改,除非对ASIC进行成本高昂且耗费时日的重新设计。

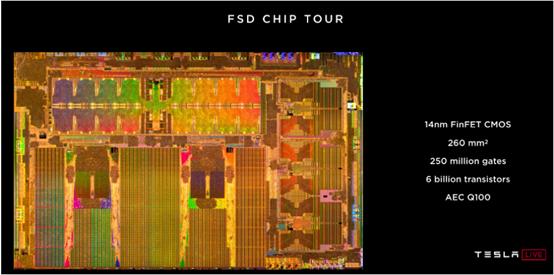

尽管存在固有风险,但是一家创新型汽车公司特斯拉(Tesla)仍然认为ASIC路线是他们提供先进安全性功能的最佳选择。特斯拉为此开发了自己的全自动驾驶(FSD)ASIC(请参阅“Tesla全自动驾驶ASIC”)。该项研发于2016年2月开始,历时29个月,直到2018年7月ASIC才获得生产认证资格。在将汽车出售给客户之前的近三年的时间里,特斯拉需要确定所需的ASIC功能。他们决定采用一种架构,其包括:

· 集成以2.5G像素/秒速率运行的摄像头接口

· 128位位宽的LPDDR4内存

· 摄像头图像信号处理器(ISP)

· H.265

· 支持FP32和FP16精度的图形处理器(GPU)

· 12个ARM A72中央处理器(CPU)

图:特斯拉全自动驾驶架构展示

面向未来的硬件

但是,如果他们认为将要使用的摄像头停产了,需要新的摄像头ISP以获得更好的微光性能,或者需要GPU来支持块浮点而不是FP32呢?这些事情可能会导致ASIC被重新设计或重大的架构改变,从而推迟其未来的车辆生产。在ASIC中构建灵活性,支持在设计周期中后期增加这些功能,以避免ASIC重新设计和推迟生产,这会不会是一个更好的方案?

在快进入到2020年的时候,我们看到汽车ASIC制造商通过开发包括嵌入式FPGA(eFPGA)半导体知识产权(IP)在内的新型ASIC架构来应对这一挑战。尽管eFPGA在2016年特斯拉开发全自动驾驶芯片时还不是主流技术,但现在已经成为主流技术了。Achronix eFPGA IP现在已在多个大批量应用中投入生产,证明Achronix拥有可实现主流生产的能力。现在,我们看到eFPGA IP正在被汽车原始设备制造商采用,以嵌入硬件可编程性,从而应对上述全新的挑战。

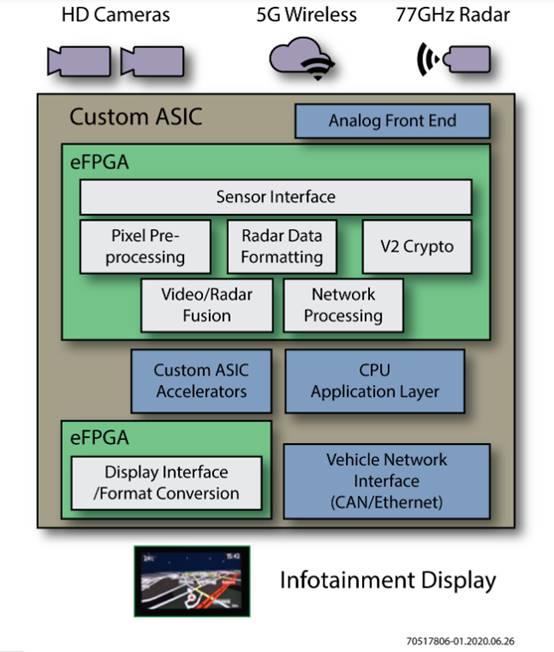

与只提供特定的逻辑密度、内存、资源组合和I/O接口的独立FPGA芯片不同,eFPGA IP解决方案可以针对特定的汽车工作负载进行完全定制。与独立的FPGA相比,eFPGA可节省高达90%的成本,并降低高达75%的功耗,同时在开发ASIC之后,还能提供同样的能力来增加新的硬件功能。例如,改变硬件规格,以提供增强的雷达和摄像头传感器融合来满足创新功能的需求,全新的、更强大的显示技术,以及全新的图像传感器功能等。下面的框图显示了集成eFPGA的ASIC可以为汽车制造商提供的一些功能。

图:基于eFPGA IP的ADAS ASIC架构

HD Cameras: 高清摄像头

5G Wireless: 5G无线

77GHz Radar: 77GHz雷达

Custom ASIC: 定制ASIC

Analog Front End: 模拟前端

eFPGA:嵌入式现场可编程逻辑门阵列

Sensor Interface: 传感器接口

Pixel Pre-processing: 像素预处理

Radar Data Formatting: 雷达数据格式整理

V2 Crypto: V2加密

Video/Radar Fusion: 视频/雷达融合

Network Processing: 网络处理

Custom ASIC Accelerators: 定制ASIC加速器

CPU Application Layer: CPU应用层Display Interface/Format Conversion: 显示界面/格式转换

Vehicle Network Interface (CAN/Ethernet): 车辆网络接口(CAN /以太网)

Infotainment Display: 信息娱乐显示

使用Achronix的Speedcore eFPGA IP技术可以实现这种架构。Speedcore eFPGA IP提供了相对于传统ASIC的竞争优势,即可帮助厂商缩短开发时间,同时允许增加全新的和创新的功能,这些功能可以在ASIC硬件架构最终确定之后进行定义。eFPGA IP确实是汽车行业的游戏规则改变者。Achronix很高兴看到eFPGA可以为未来的汽车ASIC设计带来巨大的价值。