芯片里的单位纳米是什么意思?是否是越小越先进呢?

纳米是长度单位!芯片里的单位纳米,代表芯片(处理器、半导体)制造工艺的不同工艺阶段,根据国际半导体技术蓝图(ITRS)【2017年后不再更新,继任者是被国际设备和系统路线图(IRDS)】,对半导体制程过程节点的定义如下:

芯片的技术节点(工艺节点、节点等)指一个特定的半导体制造工艺和其设计规则,不同的节点通常意味着不同的电路设计和架构。通常,技术节点越小意味着特征尺寸越小,从而生产出更小且速度更快且功率效率更高的晶体管。从这个意义上讲,越小的技术节点(纳米数小),代表着生产难度更大,所需要的工艺水平越高,自然,技术也就越先进。

芯片中的纳米意味着什么?

纳米是什么米?纳米是用于测量长度的测量单位。1纳米等于一米的十亿分之一,因此,纳米绝对不是用来测量长距离的。相反,它们用于测量极小的物体,例如现代CPU中的原子结构或晶体管,单个纳米比毫米小一百万倍。所以,纳米非常小。

芯片中晶体管是什么结构?任何芯片、IC、处理器、内存或GPU都是由大量晶体管的集成制成的。由于此类芯片是在内部集成了大量晶体管制成的,通常将其称为IC(集成电路)。并且根据制造这种芯片组的集成晶体管的数量,将它们分为SSI(小规模集成),LSI(大规模集成)或VLSI(超大规模集成)。晶体管由于集成电路(例如计算机处理器)包含微观组件,因此纳米对于测量其尺寸非常有用。实际上,纳米定义了不同的处理器时代,代表处理器(芯片)制造工艺的不同工艺阶段,这基本上是一种工艺技术,其中包括所涉及的制造工艺(如光刻)和物理参数(如尺寸和厚度)等,其中数字定义了晶体管与CPU中其他组件之间的距离。

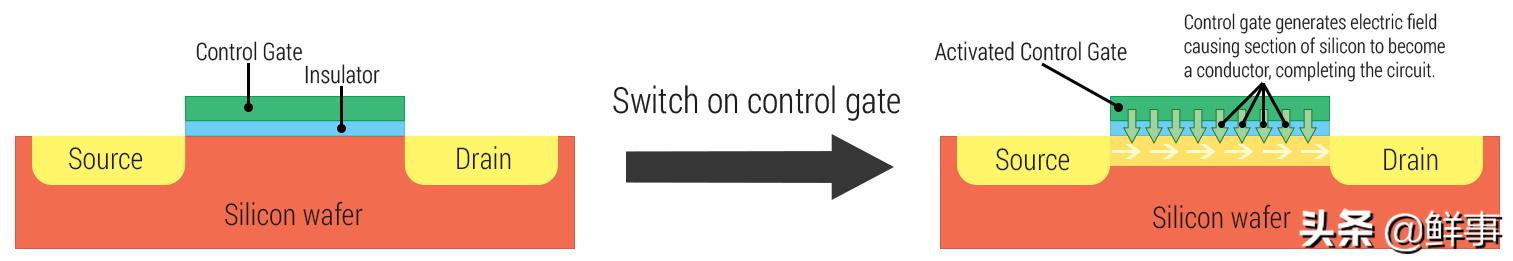

晶体管实质上由漏极(Drain),源极(Source)和栅极(Gate)组成。在源极和漏极之间有一条使电子(从而电流)流动的路径,称为通道。Gate负责控制通道的宽度。通道越宽,电子在通道中流动的速度越慢,反之亦然。处理器中提到的纳米技术是通道之间平均距离的度量。晶体管越小,源极与漏极之间的距离越小,形成栅极下方的导电沟道所需的电子或空穴的数量就越少。需要较小的输入电压以产生较少的功耗,栅极的最小宽度就是工艺制程中的X纳米。

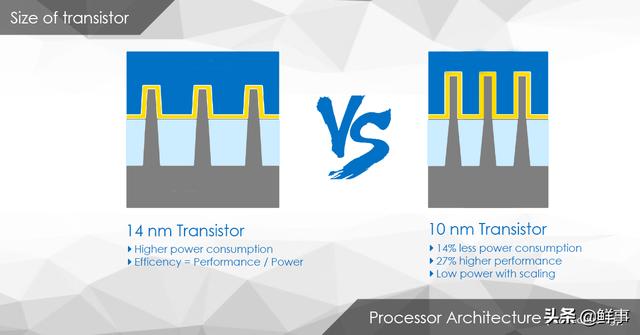

处理器架构——纳米技术:任何芯片,无论是处理器,内存还是GPU,都是通过集成大量晶体管制成的。晶体管只是电子信号的开关,具有两种状态(ON/OFF)。纳米架构是晶体管的大小。尺寸越小,可将更多晶体管嵌入到处理器芯片中,从而增加其计算量。45nm,32nm,28nm,14nm,10nm和7nm基本上是采用新制造技术的晶体管的缩放比例。芯片的长度越短,电流(或信息)可以流过的速度就越快。同样,较短的芯片消耗的电压更少。

为什么纳米小一点好?

过程节点的大小(以纳米为单位)描述了芯片最小可能元素的大小。可以这样想象:如果芯片的设计是数字图像,则一个"像素"的大小将是处理大小。制程越小,可获得的分辨率越高。制造商可以使晶体管和其他组件更小。这意味着更多的晶体管可以塞满较小的物理空间。

在给定的空间中可以容纳的晶体管越多,处理能力就越大。芯片组上使用的每个晶体管都将具有较小的尺寸。因此,可以在芯片组内部封装更多数量的晶体管,这些晶体管的尺寸与以较大纳米距离制造的芯片组的尺寸相同。如果平均缩小晶体管的所有部分,则该晶体管的电性能不会改变。

在小型芯片组中制造大量晶体管的设施可提供更多功能。

较小的晶体管速度更快,这使它们可以以更高的时钟速率工作。这样可以提高性能。这是由于计算并行性和缓存大小的增加。因此,如果希望加快芯片速度或添加新功能,则最好的办法是缩小其晶体管的尺寸。

较小的工艺也具有较低的电容,从而允许晶体管以更少的能量更快地打开和关闭。晶体管可以打开和关闭的速度越快,它的工作速度就越快。以更少的能量导通和截止的晶体管效率更高,从而降低了处理器所需的工作功率或"动态功耗"。动态功耗较低的芯片将使电池耗电更慢,运行成本更低并且更加生态友好。

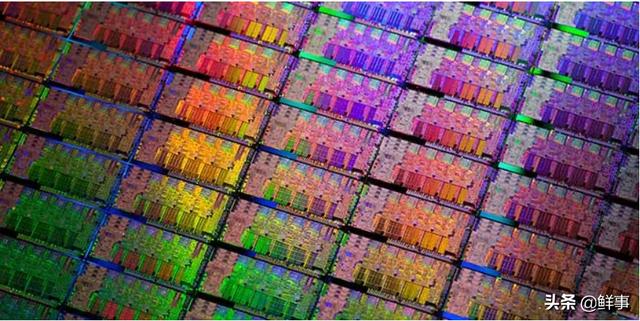

较小的芯片也更便宜。芯片是在圆形硅晶片上制成的。一个晶圆通常将包含数十个处理器管芯。较小的工艺尺寸将产生较小的管芯尺寸。而且,如果管芯尺寸较小,则可以在单个硅晶片上安装更多管芯。这导致制造效率的提高,降低了制造成本。开发新工艺确实需要大量投资,但是在收回成本之后,每个芯片的成本将大大下降。

较小的工艺规模有何弊端?

散热。尺寸较小时,由晶体管产生的热量将具有较小的散热面积,这可能会导致芯片组过热。

较小的晶体管更难制造。随着晶体管的缩小,制造以尽可能高的时钟速度运行的芯片变得越来越困难。一些芯片将无法以最高速度运行,并且这些芯片将被"绑定"或标记为具有较低时钟速度或较小缓存的芯片。较小的工艺通常会以较低的时钟速度合并更多的芯片,因为制作"完美"的芯片更具挑战性。制造商小心翼翼地消除尽可能多的问题,但这通常归因于模拟世界不可避免的变化。

较小的晶体管也具有更大的"泄漏"。泄漏是晶体管在"关"位置时允许通过多少电流的度量。这意味着随着泄漏的增加,静态功耗或晶体管空闲时消耗的电量也会增加。泄漏量更大的芯片即使在不活动时也需要更多的功率,从而更快地消耗电池并降低运行效率。

较小的过程可能会降低产量,从而导致更少的全功能芯片。这可能导致生产延迟和短缺。这使得收回开发新工艺所需的投资更加困难。这种风险因素是任何新制造工艺的基础,但对于像半导体制造这样精确的工艺而言,风险尤其如此。

为什么纳米对智能手机如此重要?

移动互联网的飞速发展,带动了半导体行业的科技进步。在芯片制造领域,智能手机芯片的制作工艺和进度,大幅度的领先于传统的PC行业,是极具代表性的产业。追求更好、更快、更小的芯片是智能手机芯片不断前行的目标,这里就纳米对智能手机的影响展开。

谈论智能手机之绕不开的话题:纳米?在智能手机的世界中,不断看到终端制造厂商互相竞争,每年都在配备最新的X纳米处理器的同时发布旗舰智能手机。旗舰产品或任何智能手机必须具备的关键功能是性能、功耗和散热,在此基础上它应具有无滞后,快速且高效的界面,而这些都与"纳米"有关。智能手机的性能取决于各种因素,例如应用程序优化、RAM大小、操作系统和处理器的优化,而这其中,处理器的性能是重中之重,芯片制程工艺的数值是旗舰机比对的关键性能指标,相当于一个水杯的容量,决定着可以装多少水。下图统计了近年来Android手机在安兔兔上的跑分,但就芯片比对而言,制程的进步的确带来了性能的飞跃(蓝色:旗舰机,黄色:中端机,红色:低端机)。

移动处理器头痛的心脏健康指数——"纳米",工艺节点越小,意味着更高的性能、更低的功耗和更高的集成度,也就意味着单位生产力更高,智能手机的心脏——芯片更强。

为什么晶体管之间的距离,纳米很重要?智能手机是便携式设备,这意味着它的空间有限,只能有限地容纳其硬件部件。所以不能使用标准的计算机和笔记本电脑处理器,因为它们的尺寸很大,这意味着需要更好的散热系统,这只会有一个结果——"空间不足!"。因此,许多公司已经开发了非常小的间距晶体管,以适合纳米面积的小型处理器,从而使其与智能手机兼容。移动处理器中的是处理器内部晶体管之间的最短距离。高通、三星、联发科、华为和苹果是为智能手机开发"纳米"移动处理器的领先公司。近年来,移动处理器中的"纳米"计数一直在从12纳米减少到10纳米再到7纳米(高通骁龙865、华为麒麟990)。纳米制造工艺术语定义了处理器的尺寸。使用20nm晶体管,可以将大约2500亿个晶体管安装在指甲大小左右的硅晶片上。比如说有一个盒子可以容纳100个大小为10cm的橡皮擦,每个橡皮擦之间相距1cm。如果减少橡皮擦之间的长度,我们可以容纳更多的橡皮擦吧?在移动处理器中的纳米后面使用类似的逻辑。同样,如果减小处理器中晶体管之间的距离,则可以安装更多的晶体管。更多的晶体管紧密堆叠在一起,这意味着在减少处理的同时电子的传播路径。这意味着更快的处理能力,更少的热量产生和低功耗。因此,移动处理器中的纳米越小,效率和功能就越强大。

高通公司的Snapdragon 855是在7纳米FinFET处理器上设计的,与10纳米芯片相比,可提供高达45%的性能提升或25%的功耗降低。

晶体管可以看做是单个处理单元,制程越小,可以在同一区域内放置的晶体管就越多,芯片中晶体管集成度就越高,从而可以进行更快,更高效的芯片设计,芯片中的晶体管数量倾向于确定芯片的处理能力。

写在最后

智能手机处理器可能无法提供PC和服务器硬件的最佳性能,但是这些小芯片在制造工艺方面一直处于业界领先地位。智能手机芯片第一个制造出了10nm和7nm尺寸的芯片,看起来它们很快也将达到5nm。先进的制造技术为提高能效,减小芯片尺寸和提高晶体管密度铺平了道路。

如果不谈论摩尔定律,就无法提及纳米和晶体管密度。简而言之,摩尔定律预言了加工技术的持续改进水平。通常将芯片收缩的速度与摩尔的预测进行比较,以衡量技术进步是否在放缓。摩尔定律是一项古老的观察,观察到芯片上的晶体管数量每年都会翻番,而成本却减半,这种情况已经维持了很长时间,但是最近一直在放缓。

缩小工艺尺寸是很困难的,但是这样做的好处是促使制造商追求越来越小的工艺尺寸。由于有了这种推动力,消费者每两年就能获得更快,更高效的芯片。这些进步使像智能手机这样的技术奇迹成为可能,并将带来下一代技术成就。